| Name of Student: |  |

|------------------|--|

| Enrollment No.:  |  |

| Class:           |  |

| Section:         |  |

| Session:         |  |

Department of Electronics & Communication Engineering

Electronic Devices Lab Manual

> Prepared By: Prof. SANKET CHOUDHARY

# LAKSHMI NARAIN COLLEGE OF TECHNOLOGY AND SCIENCE

Kalchuri Nagar, Raisen Road, Bhopal (MP) - 462023

Lakshmi Narain College of Technology & Science, Bhopal

# **Vision & Mission of the Department**

# Vision

To be world-wide recognized for adopting and keeping innovation and entrepreneurship mindset as abreast of learning to produce professionals as valuable, ethical and moral resource for industry and society.

# Mission

- To establish an ecosystem where students could grow with innovative practices followed in communication engineering.

- Adopt the global approaches to transform the young aspirant into engineering professional catering the society with ethical and patriotic zeal.

- Facilitate and felicitate the learners to have close interactions with the industry experts and researchers for keeping them updated of the current and future needs of the society.

- To develop the mindset of learners for being innovative and entrepreneurial in becoming successful professional.

# Lakshmi Narain College of Technology & Science, Bhopal

# **Program Specific Outcomes**

# (PSO's)

- To analyze, design and develop solutions of real time problems and industry needs.

- Ability of effectively communicating with the professionals and preparation of reports, documents and presentation while working in teams.

- Knowledge and understanding of latest developments in the field of VLSI, Embedded system, Networking, Matlab and other major tools necessary for keeping pace with the industry.

- Ability of solving complex engineering problems with ethical and law full approach to prevent the society and environment from adverse impacts.

# **Program Educational Objectives (PEO's)**

Student will

- The graduate will have the knowledge and skills of analog and digital communication in providing necessary solutions to the real world problems.

- The graduate will be able to design, develop, analyze and implement the modern tools and systems involving principles of electronics and telecommunication engineering.

- The graduate will be following the ethical practices of the core industry and supporting software industry in providing most acceptable solution to the society.

- The graduate will have the innovative mindset of learning and implementing the latest technological advancements and research outcomes in the electronic hardware and software to keep pace with the rapid developments in socio economic world.

# Lakshmi Narain College of Technology & Science, Bhopal

**Course: Electronic Devices (EC-304)**

**Course Outcomes (CO's)**

CO1 Analyze P N Diode and its special types based on their construction, Applications and working characteristics.

CO2 Design clipper, clamper, rectifier and voltage regulator using diode

CO3 Analysis of BJT based on their construction, working Configurations, characteristics, region of operation load line concept along with its applications.

CO4 Design of BJT as small signal and large signal amplifier.

CO5 Evaluate semiconductor devices like FET, UJT and Thyristors on the base of characteristics curve.

# **INDEX**

# Name of Student:\_\_\_\_\_Enrollment no:\_\_\_\_\_

| S.<br>No. | Title of the Experiment                                                                                                                                                                | Date of<br>Experiment | Date of<br>Submission | Remark |

|-----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|-----------------------|--------|

| 1         | To plot the V-I Characteristics of a P-N<br>Junction diode, and calculate static and<br>dynamic resistance.                                                                            |                       |                       |        |

| 2         | To plot the V-I characteristics of Zener Diode<br>in reverse bias and to verify that Zener Diode<br>acts as a Voltage Regulator.                                                       |                       |                       |        |

| 3         | To plot the V-I characteristics of Light<br>Emitting Diode (LED).                                                                                                                      |                       |                       |        |

| 4         | To observe the output waveforms and determine ripple factor of a Half Wave Rectifier with and without filter.                                                                          |                       |                       |        |

| 5         | To observe the output waveforms and determine ripple factor of a Full Wave Rectifier with and without filter.                                                                          |                       |                       |        |

| 6         | To observe and draw the input and output<br>characteristics of a transistor connected in<br>Common Base (CB) configuration and<br>calculate current gain, input and out resistance.    |                       |                       |        |

| 7         | To observe and draw the input and output<br>characteristics of a transistor connected in<br>Common Emitter (CE) configuration and<br>calculate current gain, input and out resistance. |                       |                       |        |

| 8  | To plot the frequency response of a Common<br>Emitter Transistor Amplifier and determine the<br>Bandwidth from the Response.                                                  |  |  |

|----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 9  | To plot the Drain and Transfer characteristics<br>of a given JFET and to calculate the Drain<br>Resistance $r_d$ , mutual Conductance $g_m$ &<br>Amplification factor $\mu$ . |  |  |

| 10 | To plot the V-I Characteristics of Uni-Junction<br>Transistor (UJT).                                                                                                          |  |  |

# **Code of Conducts for the Laboratories**

- > All bags must be left at the indicated place.

- > The lab timetable must be strictly followed.

- > Be **PUNCTUAL** for your laboratory session.

- ➢ Noise must be kept to a minimum.

- ➤ Workspace must be kept clean and tidy at all time.

- > Handle the experiment kit and interfacing kits with care.

- All students are liable for any damage to the accessories due to their own negligence.

- Students are strictly **PROHIBITED** from taking out any items from the laboratory.

- Students are NOT allowed to work alone in the laboratory without the Lab Supervisor

- Report immediately to the Lab Supervisor if any malfunction of the accessories, is there.

- Before leaving the lab Place the stools properly.

- Please check the laboratory notice board regularly for updates.

Date of Experiment

# **EXPERIMENT NO: 1**

**Aim**: To plot the V-I Characteristics of a P-N Junction diode, and calculate static and dynamic resistance.

| Apparatus Required: | 1. P-N Diode IN4007 - 1No.               |  |

|---------------------|------------------------------------------|--|

|                     | 2. Regulated Power supply (0-30V) - 1No. |  |

|                     | 3. Resistor $1K\Omega$ - 1No.            |  |

|                     | 4. Ammeter (0-20 mA) - 1No               |  |

|                     | 5. Ammeter (0-200µA) - 1No.              |  |

|                     | 6. Voltmeter (0-20V) - 2No.              |  |

|                     | 7. Bread board                           |  |

|                     | 8. Connecting wires                      |  |

|                     |                                          |  |

# Theory:

# (A) Forward bias operation

The P-N junction supports uni-directional current flow. If +ve terminal of the input supply is connected to anode (P-side) and –ve terminal of the input supply is connected the cathode. Then diode is said to be forward biased. In this condition the height of the potential barrier at the junction is lowered by an amount equal to given forward biasing voltage. Both the holes from p-side and electrons from n-side cross the junction simultaneously and constitute a forward current from n-side cross the junction simultaneously and constitute a forward current (injected minority current – due to holes crossing the junction and entering P- side of the diode). Assuming current flowing through the diode to be very large, the diode can be approximated as short- circuited switch.

# (B) Reverse bias operation

If negative terminal of the input supply is connected to anode (p-side) and - ve terminal of the input supply is connected to cathode (n-side) then the diode is said to be reverse biased. In this condition an amount equal to reverse biasing voltage increases the height of the potential barrier at the junction.

Both the holes on P-side and electrons on N-side tend to move away from the junction there by increasing the depleted region. However the process cannot continue indefinitely, thus a small current called reverse saturation current continues to flow in the diode. This current is negligible; the diode can be approximated as an open circuited switch.

#### **Diode current equation**

The volt-ampere characteristics of a diode explained by the following equations:

$$I = I_0 \left( e^{V/y} V_T - 1 \right)$$

where

I = current flowing in the diode,  $I_0 = reverse$  saturation current

V = Voltage applied to the diode

$V_T$  = volt- equivalent of temperature = k T/q = T/ 11,600 = 26mV

$\eta = 1$  (for Ge) and 2 (for Si)

It is observed that Ge diodes has smaller cut-in-voltage when compared to Si diode. The reverse saturation current in Ge diode is larger in magnitude when compared to silicon diode.

#### **Circuit Diagram:**

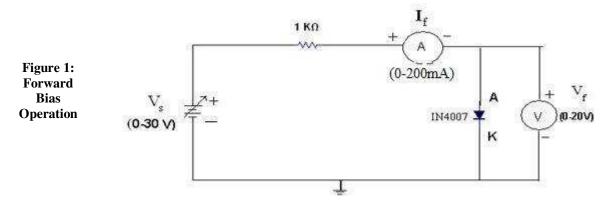

#### (A) Forward bias operation

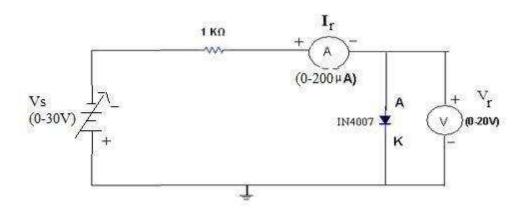

#### **(B)** Reverse bias operation

Figure 2: Reverse Bias Operation

#### **Procedure:**

#### **Forward Bias Operation**

- 1) Connect the circuit as shown in figure (1) using PN Junction diode.

- 2) Initially vary Regulated Power Supply (RPS) voltage V<sub>s</sub> in steps of **0.2** V.

- 3) Once the current starts increasing vary  $V_s$  from 1V to 10V in steps of 1V and note down the corresponding readings  $V_f$  and  $I_f$ .

- 4) Tabulate different forward currents obtained for different forward voltages.

#### **Reverse Bias Operation**

- 1) Connect the circuit as shown in figure (2) using PN Junction diode.

- 2) Vary  $V_s$  in the Regulated Power Supply (RPS) gradually in steps of **1V** from **0V** to **10V** and note down the corresponding readings  $V_r$  and  $I_r$ .

- 3) Tabulate different reverse currents obtained for different reverse voltages.

# **Observations:**

# Forward Bias Operation:

| Input Voltage<br>(Vin) | Forward<br>Voltage (V <sub>f</sub> ) | Forward<br>Current (I <sub>f</sub> ) |

|------------------------|--------------------------------------|--------------------------------------|

| 0.0                    |                                      |                                      |

| 0.2                    |                                      |                                      |

| 0.4                    |                                      |                                      |

| 0.6                    |                                      |                                      |

| 0.8                    |                                      |                                      |

| 1.0                    |                                      |                                      |

| 2.0                    |                                      |                                      |

| 3.0                    |                                      |                                      |

| 4.0                    |                                      |                                      |

| 5.0                    |                                      |                                      |

| 6.0                    |                                      |                                      |

| 7.0                    |                                      |                                      |

| 8.0                    |                                      |                                      |

| 9.0                    |                                      |                                      |

| 10.0                   |                                      |                                      |

# **Reverse Bias Operation:**

| Input Voltage<br>(Vin) | Reverse<br>Voltage (Vr) | Reverse<br>Current (I <sub>r</sub> ) |

|------------------------|-------------------------|--------------------------------------|

| 1.0                    |                         |                                      |

| 2.0                    |                         |                                      |

| 3.0                    |                         |                                      |

| 4.0                    |                         |                                      |

| 5.0                    |                         |                                      |

| 6.0                    |                         |                                      |

| 7.0                    |                         |                                      |

| 8.0                    |                         |                                      |

| 9.0                    |                         |                                      |

| 10.0                   |                         |                                      |

Plot the graph on the graph paper

Page 12

# Electronics Devices Lab Manual

Calculations from Graph:

Static forward Resistance  $= \frac{V_f}{I_f} \Omega$  $R_t$

Dynamic Forward Resistance  $r_{\alpha} = \frac{\Delta V_f}{\Delta I_f} \Omega$

**<u>Result:</u>** Volt-Ampere Characteristics of P-N Diode are studied.

| The Cut in Voltage or Knee Voltage (Vy) of 1N4007 | _Volts. |

|---------------------------------------------------|---------|

| The Dynamic Forward resistance of 1N4007 is       | Ω.      |

The Static Forward resistance of 1N4007 is  $\Omega$  .

# **Signature of Faculty**

Date of Experiment

#### **EXPERIMENT NO: 2**

**Aim**: To plot the V-I characteristics of Zener Diode in reverse bias and to verify that Zener Diode acts as a Voltage Regulator.

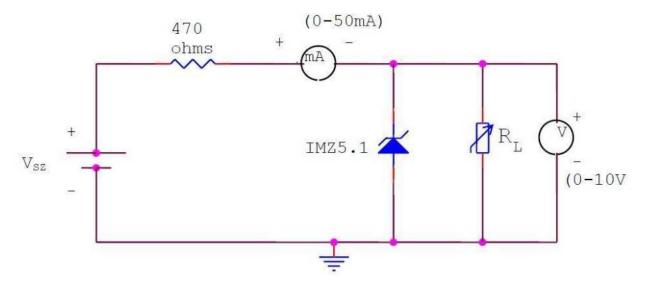

**Apparatus Required**: 1. Zener diode IMZ5.1 V.

- 2. 470 $\Omega$  resistor.

- 3. Ammeter (0-50mA).

- 4. Voltmeter (0-10V).

- 5. RPS (0-30V).

- 6. Bread Board.

- 7. Decade Resistance Box (DRB).

- 8. Connecting Wires.

**Theory**: A Zener diode is heavily doped p-n junction diode, specially made to operate in the break down region. A p-n junction diode normally does not conduct when reverse biased. But if the reverse bias is increased, at a particular voltage it starts conducting heavily. This voltage is called Break down Voltage. High current through the diode can permanently damage the device.

To avoid high current, we connect a resistor in series with Zener diode. Once the diode starts conducting it maintains almost constant voltage across the terminals whatever may be the current through it, i.e., it has very low dynamic resistance. It is used in voltage regulators.

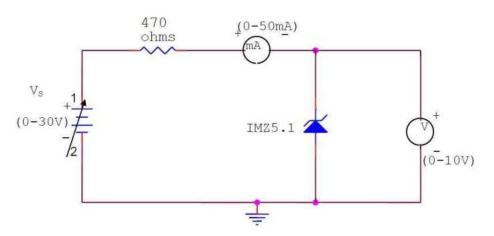

#### **V-I Characteristics**

**Procedure:** 1. Make the connections as shown in the circuit diagram.

2. Vary the RPS voltage from 0V to 30V in steps of 1V.

3. Tabulate the readings of Ammeter  $(I_Z)$  and Voltmeter  $(V_Z)$ .

- 4. Plot the graph between  $V_Z \& I_Z$ .

- 5. Calculate the break down voltage of given Zener diode from the graph

# **Circuit Diagram:**

#### **Observation Table:**

| Sr. No | V <sub>s</sub> (volts) | V <sub>z</sub> (volts) | Iz (volts) |

|--------|------------------------|------------------------|------------|

| 1      | 1 V                    |                        |            |

| 2      | 2 V                    |                        |            |

| 3      | 3 V                    |                        |            |

| 4      | 4 V                    |                        |            |

| 5      | 5 V                    |                        |            |

| 6      | 6 V                    |                        |            |

| 7      | 7 V                    |                        |            |

| 8      | 8 V                    |                        |            |

| 9      | 9 V                    |                        |            |

| 10     | 10 V                   |                        |            |

#### **Voltage Regulator:**

**Procedure:** 1. Make the connections as shown in figure 2.

2. Measure VNL (No load voltage) by opening the load resistance.

3. Connect the load resistance, and vary the load resistance from  $1000\Omega$  to  $100\Omega$  in steps of  $100\Omega$  and note down the readings of Voltmeter (VZ) and Ammeter (IS).

1. Calculate % Regulation by using the formula given below. % Regulation =  $\frac{V_{NL} - V_L}{V_{NL}} \times 100\%$

## **Circuit Diagram:**

#### **Observation Table:**

V<sub>NL</sub> =\_\_\_\_volts

| Sr. No. | R <sub>L</sub> (ohms) | V <sub>L</sub> (volts) | $I_{S} (I_{z}+I_{L}) (mA)$ | % Regulation |

|---------|-----------------------|------------------------|----------------------------|--------------|

| 1       | 1000                  |                        |                            |              |

| 2       | 900                   |                        |                            |              |

| 3       | 800                   |                        |                            |              |

| 4       | 700                   |                        |                            |              |

| 5       | 600                   |                        |                            |              |

| 6       | 500                   |                        |                            |              |

| 7       | 400                   |                        |                            |              |

| 8       | 300                   |                        |                            |              |

| 9       | 200                   |                        |                            |              |

| 10      | 100                   |                        |                            |              |

# Plot the graph on graph paper

#### **Result:**

- 1. The Zener breakdown voltage = \_\_\_\_\_volts

- 2. The reverse bias characteristics of Zener diode are observed and plotted on the graph.

- 3. The Regulation characteristics of a Zener Diode are observed and plotted on the graph.

# **Signature of Faculty**

Date of Experiment

## **EXPERIMENT NO: 3**

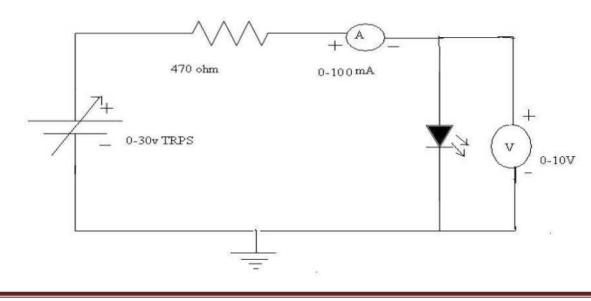

Aim: To plot the V-I characteristics of Light Emitting Diode (LED).

Apparatus Required: 1. L.E.D

- $2.470\Omega$  resistor

- 3. Ammeter (0-100ma)

- 4. Voltmeter (0-20v)

- 5. RPS

- 6. Bread board

- 7. Connecting wires

**Theory:** The "**Light Emitting Diode**" or LED as it is more commonly called, is basically just a specialised type of diode as they have very similar electrical characteristics to a PN junction diode. This means that an LED will pass current in its forward direction but block the flow of current in the reverse direction.

**Light Emitting Diodes** are made from exotic semiconductor compounds such as Gallium Arsenide (GaAs), Gallium Phosphide (GaP), Gallium Arsenide Phosphide (GaAsP), Silicon Carbide (SiC) or Gallium Indium Nitride (GaInN) all mixed together at different ratios to produce a distinct wavelength of colour.

## **Circuit Diagram:**

# **Procedure:**

1. Connections must be made as per the circuit diagram.

2. By varying the voltage in steps corresponding current in the ammeter is noted.

3. At the same time the glow intensity of the light emitting diode is also to be noted.

4. Taking voltage on X-axis and current on Y-axis that gives the forward bias V-I characteristics, plot a graph.

#### **Observation Table:**

| Sr. No. | V <sub>s</sub> (volts) | V <sub>f</sub> (volts) | I <sub>f</sub> (volts) | Intensity of glow |

|---------|------------------------|------------------------|------------------------|-------------------|

| 1       |                        |                        |                        |                   |

| 2       |                        |                        |                        |                   |

| 3       |                        |                        |                        |                   |

| 4       |                        |                        |                        |                   |

| 5       |                        |                        |                        |                   |

| 6       |                        |                        |                        |                   |

| 7       |                        |                        |                        |                   |

| 8       |                        |                        |                        |                   |

| 9       |                        |                        |                        |                   |

| 10      |                        |                        |                        |                   |

**Result:** The forward characteristics of a light emitting diode are obtained and plotted in graph paper.

**Signature of Faculty**

Signature of Faculty

Date of Experiment

# **EXPERIMENT NO: 4**

**Aim**: To observe the output waveforms and determine ripple factor of a Half Wave Rectifier with and without filter.

**Apparatus Required**: 1. 230-12V Step down Transformer – 1no.

- 2. IN 4007 Diode 1no.

- 3. 0-20V Voltmeter /DMM 1no.

- 4. 0-100mA Millimeter/DMM 1no.

- 5. 1K $\Omega$ , 2K $\Omega$ , 10K $\Omega$  resistor 1each.

- 6.  $100\mu f/25V$  capacitor -1 no.

- 7. Bread Board.

- 8. Connecting wires.

**Theory:** In Half Wave Rectification, When AC supply is applied at the input, only Positive Half Cycle appears across the load whereas, the negative Half Cycle is suppressed. How this can be explained as follows:

During positive half-cycle of the input voltage, the diode  $D_1$  is in forward bias and conducts through the load resistor  $R_L$ . Hence the current produces an output voltage across the load resistor  $R_L$ , which has the same shape as the +ve half cycle of the input voltage.

During the negative half-cycle of the input voltage, the diode is reverse biased and there is no current through the circuit. i.e., the voltage across  $R_L$  is zero. The net result is that only the +ve half cycle of the input voltage appears across the load. The average value of the half wave rectified o/p voltage is the value measured on dc voltmeter.

# **Theoretical calculations for Ripple factor:**

## Without Filter:

$$V_{rms} = \frac{V_m}{2} \text{ or } V_m = 2V_{rms}$$

$$V_{dc} = \frac{V_m}{\pi}$$

Ripple factor =

$$\sqrt{\left(\frac{V_{rms}}{V_{dc}}\right)^2 - 1}$$

With Filter:

Ripple factor =

$$\frac{1}{2\sqrt{3}fR_LC}$$

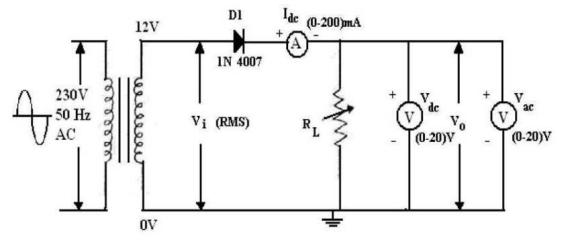

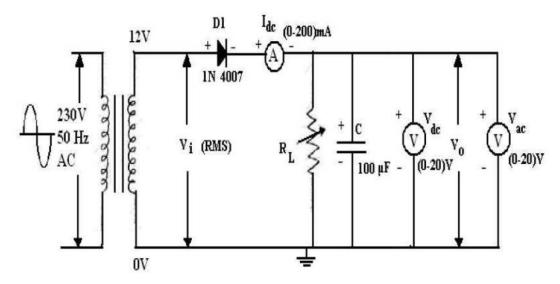

**Circuit Diagram:**

# Half Wave Rectifier without Filter:

Figure a: Half Wave Rectifier without filter Half Wave Rectifier with Filter

Figure b: Half Wave Rectifier with filter

## **Procedure:**

1. Connect the circuit as shown in figure (a).

2. Adjust the load resistance,  $R_L$  to 500 $\Omega$ , and note down the readings of input and output voltages through oscilloscope.

3. Note the readings of dc current, dc voltage and ac voltage.

4. Now, change the resistance the load resistance,  $R_L$  to 1 K $\Omega$  and repeat the procedure as above. Also repeat for 10 K $\Omega$ .

5. Readings are tabulated as per the tabular column.

6. Connect the circuit as shown in figure (b) and repeat the procedure.

#### **Observation Table:**

#### Half Wave Rectifier without Filter

| Sr.<br>No. | RL<br>(ohms) | Average<br>DC current<br>(I <sub>dc</sub> ) | Average<br>DC voltage<br>(V <sub>dc</sub> ) | RMS<br>voltage<br>(Vac) | Ripple<br>factor<br>(V <sub>ac</sub> /V <sub>dc</sub> ) |

|------------|--------------|---------------------------------------------|---------------------------------------------|-------------------------|---------------------------------------------------------|

| 1          | 1K           |                                             |                                             |                         |                                                         |

| 2          | 2K           |                                             |                                             |                         |                                                         |

| 3          | 10K          |                                             |                                             |                         |                                                         |

Half Wave Rectifier with Filter with  $C = 100 \mu F$

| Sr. | RL     | Average            | Average            | RMS                | Ripple                              |

|-----|--------|--------------------|--------------------|--------------------|-------------------------------------|

| No. | (ohms) | DC current         | DC voltage         | voltage            | factor                              |

|     |        | (I <sub>dc</sub> ) | (V <sub>dc</sub> ) | (V <sub>ac</sub> ) | (V <sub>ac</sub> /V <sub>dc</sub> ) |

| 1   | 1K     |                    |                    |                    |                                     |

| 2   | 2K     |                    |                    |                    |                                     |

| 3   | 10K    |                    |                    |                    |                                     |

#### **Result:**

1. Input and Output waveforms of a half-wave with /without filter are observed and plotted.

2. For Half-wave rectifier without filter:-

Ripple factor at  $1K\Omega =$ \_\_\_\_,  $2K\Omega =$ \_\_\_\_,  $10 K\Omega =$ \_\_\_\_.

3. For Half-wave rectifier with filter:-

Ripple factor at  $1K\Omega$ ,  $100\mu F = 2K\Omega$ ,  $100\mu F =$

10 KΩ,  $100\mu$ F =

**Signature of Faculty**

Date of Experiment

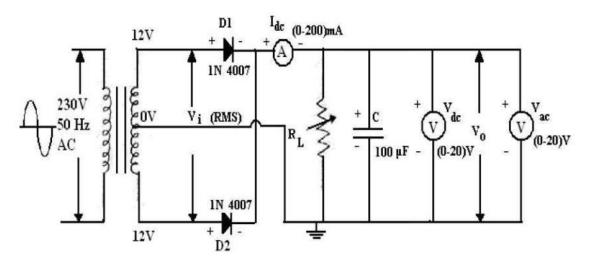

#### **EXPERIMENT NO: 5**

**Aim**: To observe the output waveforms and determine ripple factor of a Full Wave Rectifier with and without filter.

Apparatus Required: 1. 230-12V Centre tapped Step down Transformer

- 2. IN 4007 Diode 2no.

- 3. 0-20V Voltmeter /DMM 1no.

- 4. 0-100mA Millimeter/DMM 1no.

- 5. 1K $\Omega$ , 2K $\Omega$ , 10K $\Omega$  resistor 1each.

- 6.  $100\mu f/25V$  capacitor 1no.

- 7. Bread Board.

- 8. Connecting wires.

**Theory:** The circuit of a center-tapped full wave rectifier uses two diodes  $D_1$  &  $D_2$ . During positive half cycle of secondary voltage (input voltage), the diode  $D_1$  is forward biased and  $D_2$  is reverse biased.

The diode  $D_1$  conducts and current flows through load resistor  $R_L$ . During negative half cycle, diode  $D_2$  becomes forward biased and  $D_1$  reverse biased. Now,  $D_2$  conducts and current flows through the load resistor RL in the same direction. There is a continuous current flow through the load resistor RL, during both the half cycles and will get unidirectional current as show in the model graph. The difference between full wave and half wave rectification is that a full wave rectifier allows unidirectional (one way) current to the load during the entire 360 degrees of the input signal and half-wave rectifier allows this only during one half cycle (180 degree).

#### **Theoretical calculations for Ripple factor:**

Without Filter:

$$V_{rms} = \frac{V_m}{\sqrt{2}} \text{ or } V_m = \sqrt{2}V_{rms}$$

$$V_{dc} = \frac{2V_m}{\pi}$$

Ripple factor =

$$\sqrt{\left(\frac{V_{rms}}{V_{dc}}\right)^2 - 1}$$

With Filter:

Ripple factor =

$$\frac{1}{2\sqrt{3}fR_LC}$$

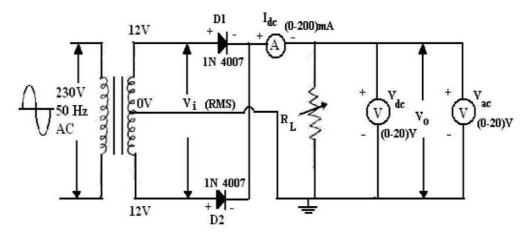

**Circuit Diagram:**

**Full Wave Rectifier without Filter:**

Full Wave Rectifier with Filter:

# **Procedure:**

1. Connect the circuit as shown in the figure (a).

2. Adjust the load resistance  $R_L$  to  $1K\Omega$  and note the readings of input and output voltages through Oscilloscope.

3. Note the readings of DC current, DC voltage and AC voltage.

4. Now change the load resistance RL to  $2K\Omega$  and repeat the procedure as the above.

5. Readings are tabulate as per the tabular column.

6. Connect a capacitor of  $100\mu$ F values in parallel with the load and repeat the above procedure.

#### **Observation Table:**

| Full Wave Rectifier without Filter | Full | Wave | Rectifier | without | Filter |

|------------------------------------|------|------|-----------|---------|--------|

|------------------------------------|------|------|-----------|---------|--------|

| Sr. | R <sub>L</sub> | Average            | Average            | RMS                | Ripple                              |

|-----|----------------|--------------------|--------------------|--------------------|-------------------------------------|

| No. | (ohms)         | DC current         | 0                  | voltage            | factor                              |

|     |                | (I <sub>dc</sub> ) | (V <sub>dc</sub> ) | (V <sub>ac</sub> ) | (V <sub>ac</sub> /V <sub>dc</sub> ) |

| 1   | 1K             |                    |                    |                    |                                     |

| 2   | 2K             |                    |                    |                    |                                     |

| 3   | 10K            |                    |                    |                    |                                     |

#### Full Wave Rectifier with Filter with $C = 100 \mu F$

| Sr. | RL     | Average            | Average            | RMS                | Ripple            |

|-----|--------|--------------------|--------------------|--------------------|-------------------|

| No. | (ohms) | DC current         | DC voltage         | voltage            | factor            |

|     |        | (I <sub>dc</sub> ) | (V <sub>dc</sub> ) | (V <sub>ac</sub> ) | $(V_{ac}/V_{dc})$ |

| 1   | 1K     |                    |                    |                    |                   |

| 2   | 2K     |                    |                    |                    |                   |

| 3   | 10K    |                    |                    |                    |                   |

#### **Result:**

1. Input and Output waveforms of a Full-wave with /without filter are observed and plotted.

2. For Full-wave rectifier without filter:-

Ripple factor at  $1K\Omega =$ \_\_\_\_,  $2K\Omega =$ \_\_\_\_,  $10 K\Omega =$ \_\_\_\_.

3. For Full-wave rectifier with filter:-

Ripple factor at  $1K\Omega$ ,  $100\mu F =$  $2K\Omega$ ,  $100\mu F =$ 10 KΩ,  $100\mu$ F =

Signature of Faculty

Date of Experiment

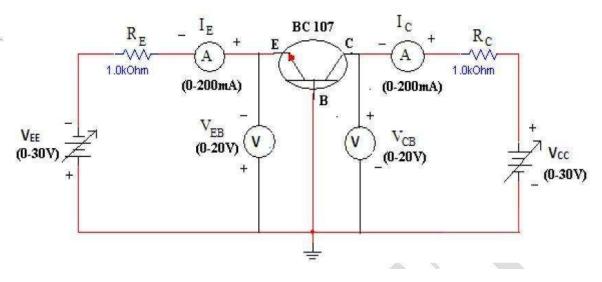

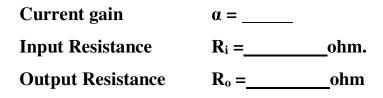

#### **EXPERIMENT NO: 6**

**Aim**: To observe and draw the input and output characteristics of a transistor connected in Common Base (CB) configuration and calculate current gain, input and out resistance.

**Apparatus Required**: 1. Transistor, BC107 -1No.

- 2. Regulated power supply (0-30V) -2No.

- 3. Voltmeter (0-20V) 2No.

- 4. Ammeters (0-20mA) 2No.

- 5. Resistor,  $1K\Omega 2No$

- 6. Bread Board.

- 7. Connecting wires.

**Theory:** A transistor is a three terminal active device. The terminals are emitter, base, collector. In CB configuration, the base is common to both input (emitter) and output (collector). For normal operation, the E-B junction is forward biased and C-B junction is reverse biased.

With an increasing the reverse collector voltage, the space-charge width at the output junction increases and the effective base width 'W' decreases. This phenomenon is known as "Early effect". Then, there will be less chance for recombination within the base region. With increase of charge gradient with in the base region, the current of minority carriers injected across the emitter junction increases.

The current amplification factor of CB configuration is given by,

$$a = \frac{\Delta I_{C}}{\Delta I_{E}}$$

Input Resistance  $R_{i} = \frac{\Delta V_{BE}}{\Delta I_{E}}$  at constant  $V_{CB}$

Output Resistance  $R_{o} = \frac{\Delta V_{CB}}{\Delta I_{C}}$  at constant  $I_{E}$

#### **Circuit Diagram:**

## **Procedure:**

## **Input Characteristics:**

1. Connections are made as per the circuit diagram.

2. For plotting the input characteristics, the output voltage  $V_{CE}$  is kept constant at 0V and for different values of  $V_{EE}$  note down the values of  $I_E$  and  $V_{BE}$ .

3. Repeat the above step keeping  $V_{CB}$  at 2V, 4V, and 6V and all the readings are tabulated.

4. A graph is drawn between  $V_{EB}$  and  $I_E$  for constant  $V_{CB}$ .

## **Output Characteristics:**

1. Connections are made as per the circuit diagram.

2. For plotting the output characteristics, the input  $I_E$  is kept constant at 0.5mA and for different values of  $V_{CC}$ , note down the values of  $I_C$  and  $V_{CB}$ .

3. Repeat the above step for the values of  $I_E$  at 1mA, 5mA and all the readings are tabulated.

4. A graph is drawn between  $V_{CB}$  and  $I_C$  for constant  $I_E$ .

# **Observation:**

# **Input Characteristics:**

| Sr. | $V_{CB} =$          |                     | $V_{CB} =$          |                     | $V_{CB} =$          |                     |

|-----|---------------------|---------------------|---------------------|---------------------|---------------------|---------------------|

| No. | V <sub>EB</sub> (V) | I <sub>E</sub> (mA) | V <sub>EB</sub> (V) | I <sub>E</sub> (mA) | V <sub>EB</sub> (V) | I <sub>E</sub> (mA) |

| 1   |                     |                     |                     |                     |                     |                     |

| 2   |                     |                     |                     |                     |                     |                     |

| 3   |                     |                     |                     |                     |                     |                     |

| 4   |                     |                     |                     |                     |                     |                     |

| 5   |                     |                     |                     |                     |                     |                     |

| 6   |                     |                     |                     |                     |                     |                     |

| 7   |                     |                     |                     |                     |                     |                     |

| 8   |                     |                     |                     |                     |                     |                     |

| 9   |                     |                     |                     |                     |                     |                     |

| 10  |                     |                     |                     |                     |                     |                     |

# **Output Characteristics:**

| Sr. | $I_E =$             |                     | IE                  | $I_E =$             |                     | =                   |

|-----|---------------------|---------------------|---------------------|---------------------|---------------------|---------------------|

| No. | V <sub>CB</sub> (V) | I <sub>C</sub> (mA) | V <sub>CB</sub> (V) | I <sub>C</sub> (mA) | V <sub>CB</sub> (V) | I <sub>C</sub> (mA) |

| 1   |                     |                     |                     |                     |                     |                     |

| 2   |                     |                     |                     |                     |                     |                     |

| 3   |                     |                     |                     |                     |                     |                     |

| 4   |                     |                     |                     |                     |                     |                     |

| 5   |                     |                     |                     |                     |                     |                     |

| 6   |                     |                     |                     |                     |                     |                     |

| 7   |                     |                     |                     |                     |                     |                     |

| 8   |                     |                     |                     |                     |                     |                     |

| 9   |                     |                     |                     |                     |                     |                     |

| 10  |                     |                     |                     |                     |                     |                     |

# Graph is plotted on graph paper

**Result:** The input and output characteristics of transistor in CB configuration is observed and the plotted on graph paper.

# **Signature of Faculty**

Date of Experiment

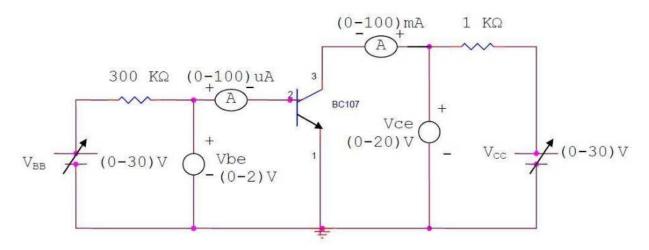

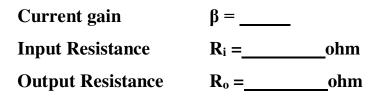

#### **EXPERIMENT NO: 7**

**Aim**: To observe and draw the input and output characteristics of a transistor connected in Common Emitter (CE) configuration and calculate current gain, input and out resistance.

**Apparatus Required**: 1. Transistor, BC107 -1No.

- 2. Regulated power supply (0-30V) -2No.

- 3. Voltmeter (0-20V) 2No.

- 4. Ammeters (0-20mA) 1No.

- 5. Ammeters (0-200µA) 1No.

- 6. Resistor,  $100\Omega$ ,  $1K\Omega 1$  each

- 7. Bread Board.

- 8. Connecting wires.

**Theory:** In common emitter configuration, input voltage is applied between base and emitter terminals and output is taken across the collector and emitter terminals. Therefore the emitter terminal is common to both input and output.

The input characteristics resemble that of a forward biased diode curve. This is expected since the Base-Emitter junction of the transistor is forward biased. As compared to CB arrangement  $I_B$  increases less rapidly with  $V_{BE}$ . Therefore input resistance of CE circuit is higher than that of CB circuit.

The output characteristics are drawn between  $I_C$  and  $V_{CE}$  at constant  $I_B$  the collector current varies with  $V_{CE}$  up to few volts only. After this the collector current becomes almost constant, and independent of  $V_{CE}$ . The value of  $V_{CE}$  up to which the collector current changes with  $V_{CE}$  is known as Knee voltage. The transistor always operated in the region above Knee voltage,  $I_C$  is always constant and is approximately equal to  $I_B$ . The current amplification factor of CE configuration is given by

$$Q = \frac{\Delta I_{C}}{\Delta I_{B}}$$

Input Resistance

$$R_i = \frac{\Delta V_{BE}}{\Delta I_B}$$

at constant  $V_{CE}$

Output Resistance  $R_o = \frac{\Delta V_{CB}}{\Delta I_C}$  at constant  $I_B$

**Circuit Diagram:**

#### **Procedure:**

## **Input Characteristics:**

1. Connect the circuit as per the circuit diagram.

2. For plotting the input characteristics the output voltage  $V_{CE}$  is kept constant at 1V and for different values of  $V_{BB}$ , note down the values of  $I_B$  and  $V_{BE}$

3. Repeat the above step by keeping  $V_{CE}$  at 2V and 4V and tabulate all the readings.

4. Plot the graph between  $V_{BE}$  and  $I_B$  for constant  $V_{CE}$ .

## **Output Characteristics:**

1. Connect the circuit as per the circuit diagram

2. For plotting the output characteristics the input current  $I_B$  is kept constant at 50µA and for different values of  $V_{CC}$  note down the values of  $I_C$  and  $V_{CE}$

3. Repeat the above step by keeping  $I_B$  at 75  $\mu A$  and 100  $\mu A$  and tabulate the all the readings

4. Plot the graph between  $V_{CE}$  and  $I_C$  for constant  $I_B$ .

# **Observation:**

# **Input Characteristics:**

| Sr. | $V_{CE} =$          |                     | Vc                  | $\mathbf{V}_{\mathbf{CE}} =$ |                     | Е =                 |

|-----|---------------------|---------------------|---------------------|------------------------------|---------------------|---------------------|

| No. | V <sub>BE</sub> (V) | I <sub>B</sub> (µA) | V <sub>BE</sub> (V) | $I_B(\mu A)$                 | V <sub>BE</sub> (V) | I <sub>B</sub> (µA) |

| 1   |                     |                     |                     |                              |                     |                     |

| 2   |                     |                     |                     |                              |                     |                     |

| 3   |                     |                     |                     |                              |                     |                     |

| 4   |                     |                     |                     |                              |                     |                     |

| 5   |                     |                     |                     |                              |                     |                     |

| 6   |                     |                     |                     |                              |                     |                     |

| 7   |                     |                     |                     |                              |                     |                     |

| 8   |                     |                     |                     |                              |                     |                     |

| 9   |                     |                     |                     |                              |                     |                     |

| 10  |                     |                     |                     |                              |                     |                     |

# **Output Characteristics:**

| Sr. | $I_B =$     |                     | IB                  | $I_B =$             |             | =                   |

|-----|-------------|---------------------|---------------------|---------------------|-------------|---------------------|

| No. | $V_{CE}(V)$ | I <sub>C</sub> (mA) | V <sub>CE</sub> (V) | I <sub>C</sub> (mA) | $V_{CE}(V)$ | I <sub>C</sub> (mA) |

| 1   |             |                     |                     |                     |             |                     |

| 2   |             |                     |                     |                     |             |                     |

| 3   |             |                     |                     |                     |             |                     |

| 4   |             |                     |                     |                     |             |                     |

| 5   |             |                     |                     |                     |             |                     |

| 6   |             |                     |                     |                     |             |                     |

| 7   |             |                     |                     |                     |             |                     |

| 8   |             |                     |                     |                     |             |                     |

| 9   |             |                     |                     |                     |             |                     |

| 10  |             |                     |                     |                     |             |                     |

### Graph is plotted on graph paper

**Result:** The input and output characteristics of transistor in CE configuration is observed and the plotted on graph paper.

**Signature of Faculty**

Date of Experiment

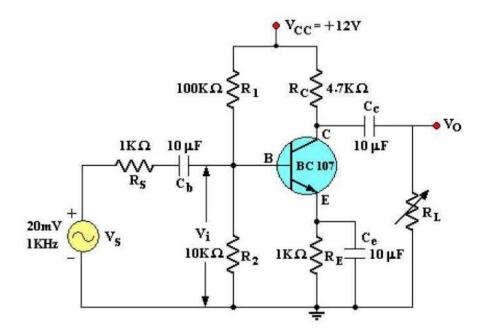

#### **EXPERIMENT NO: 8**

**Aim**: To plot the frequency response of a Common Emitter Transistor Amplifier and determine the Bandwidth from the Response.

**Apparatus Required**: 1. Transistor BC107 -1No.

- 2. Regulated power Supply (0-30V) -1No.

- 3. Function Generator -1No.

- 4. CRO -1No.

- 5. Resistors [1K (2), 4.7K (1), 10K (2), 100K (1)]

- 6. Capacitors,  $10\mu$ F -3No.

- 7. Bread Board

- 8. Connecting wires.

**Theory:** The CE amplifier provides high gain & wide frequency response. The emitter lead is common to both input & output circuits and is grounded. The emitter-base circuit is forward biased. The collector current is controlled by the base current rather than emitter current. When a transistor is biased in active region it acts like an amplifier. The input signal is applied to base terminal of the transistor and amplifier output is taken across collector terminal. A very small change in base current produces a much larger change in collector current. When positive half-cycle is fed to the input circuit, it opposes the forward bias of the circuit which causes the collector current to decrease; it decreases the voltage more negative. Thus when input cycle varies through a negative half-cycle, increases the forward bias of the circuit, which causes the collector current to increases thus the output signal is common emitter amplifier is in out of phase with the input signal. An amplified output signal is obtained when this fluctuating collector current flows through a collector  $R_c$ .

The capacitor across the collector resistor  $R_C$  will act as a bypass capacitor. This will improve high frequency response of amplifier.

#### **Circuit Diagram:**

#### **Procedure:**

1. Connect the circuit as shown in figure, apply  $V_{CC}$  of 12 Volts DC.

2. Apply I/P Voltage of 20mV at 1KHz from the Signal Generator and observe the O/P on CRO.

3. Vary the frequency from 100 Hz to 1MHz in appropriate steps and note down the corresponding O/P Voltage Vo in a tabular form.

4. Calculate the Voltage Gain  $A_v = V_o/V_s$  and note down in the tabular form.

5. Plot the frequency (f) V/s Gain  $(A_v)$  on a Semi-log Graph paper.

6. Mark the lower cutoff frequency ( $f_L$ ) and higher cutoff frequency ( $f_H$ ) at 70.7% of maximum gain point. And calculate the Bandwidth BW =  $f_H - f_L$ .

**Observation:**

| Signal Voltage Vs =volts |                          |                              |                      |                                           |  |  |  |

|--------------------------|--------------------------|------------------------------|----------------------|-------------------------------------------|--|--|--|

| Sr.<br>No.               | Signal Frequency<br>(Hz) | Output Voltage<br>Vo (volts) | $Gain A_v = V_0/V_s$ | decibel Gain<br>20log(A <sub>v</sub> ) dB |  |  |  |

| 1                        | 100 Hz                   |                              |                      |                                           |  |  |  |

| 2                        | 200 Hz                   |                              |                      |                                           |  |  |  |

| 3                        | 500 Hz                   |                              |                      |                                           |  |  |  |

| 4                        | 1K Hz                    |                              |                      |                                           |  |  |  |

| 5                        | 2K Hz                    |                              |                      |                                           |  |  |  |

| 6                        | 5K Hz                    |                              |                      |                                           |  |  |  |

| 7                        | 10K Hz                   |                              |                      |                                           |  |  |  |

| 8                        | 20K Hz                   |                              |                      |                                           |  |  |  |

| 9                        | 50K Hz                   |                              |                      |                                           |  |  |  |

| 10                       | 100K Hz                  |                              |                      |                                           |  |  |  |

| 11                       | 200K Hz                  |                              |                      |                                           |  |  |  |

| 12                       | 500K Hz                  |                              |                      |                                           |  |  |  |

| 13                       | 1M Hz                    |                              |                      |                                           |  |  |  |

## **Result:**

| Lower cutoff frequency $(f_L)$  | = | _Hz |

|---------------------------------|---|-----|

| Higher cutoff frequency $(f_H)$ | = | Hz  |

| Bandwidth (BW)                  | = | Hz  |

## Graph is plotted on graph paper

Signature of Faculty

## Electronics Devices Lab Manual

Date of Experiment

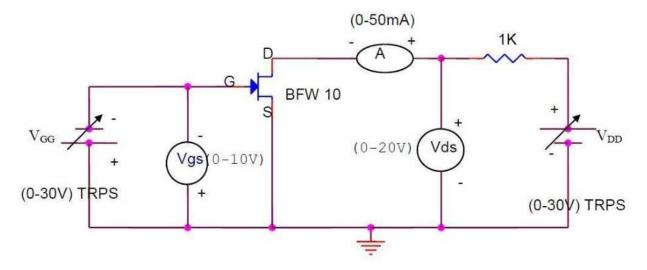

**EXPERIMENT NO: 9**

Aim: To plot the Drain and Transfer characteristics of a given JFET and to calculate the Drain Resistance  $r_d$ , mutual Conductance  $g_m$  & Amplification factor  $\mu$ .

Apparatus Required: 1. RPS (0-30v) - 2no.

- 2. Voltmeters (0-2)V & (0-20)V

- 3. JFET BFW10

- 4. Resistance 1K

- 5. Connecting wires

- 6. Bread board

**Theory:** A FET is a three terminal device, in which current conduction is by majority carriers only. The flow of current is controlled by means of an Electric field. The three terminals of FET are Gate, Drain and Source. It is having the characteristics of high input impedance and less noise, the Gate to Source junction of the FETs always reverse biased. In response to small applied voltage from drain to source, the n-type bar acts as sample resistor, and the drain current increases linearly with V<sub>DS</sub>. With increase in I<sub>D</sub> the ohmic voltage drop between the source and the channel region reverse biases the junction and the conducting position of the channel begins to remain constant. The V<sub>DS</sub> at this instant is called "pinch of voltage". If the gate to source voltage (V<sub>GS</sub>) is applied in the direction to provide additional reverse bias, the pinch off voltage will is decreased. In amplifier application, the FET is always used in the region beyond the pinch-off.

#### **FET parameters:**

AC Drain Resistance

$$r_{d} = \frac{\Delta V_{DS}}{\Delta I_{D}}$$

at constant  $V_{GS}$

Transconductance  $g_{m} = \frac{\Delta I_{D}}{\Delta V_{GS}}$  at constant  $V_{DS}$

Amplicaton factor  $\mu = \frac{\Delta V_{DS}}{\Delta V_{GS}}$  at constant  $I_{D}$

The relation between above parameters is given by

$$\mu = r_d \times g_m$$

The drain current is given by

$$I_D = I_{DSS} \left(1 - \frac{V_{GS}}{V_P}\right)^2$$

#### **Circuit Diagram:**

#### **Procedure:**

- 1. All the connections are made as per the circuit diagram.

- 2. To plot the drain characteristics, keep VGS constant at 0V.

- 3. Vary the VDD and observe the values of VDS and ID.

- 4. Repeat the above steps 2, 3 for different values of VGS at 0.1V and 0.2V.

- 5. All the readings are tabulated.

- 6. To plot the transfer characteristics, keep VDS constant at 1V.

- 7. Vary VGG and observe the values of VGS and ID.

- 8. Repeat steps 6 and 7 for different values of VDS at 1.5 V and 2V.

- 9. The readings are tabulated.

- 10. From drain characteristics, calculate the values of dynamic resistance (r<sub>d</sub>)

- 11. From transfer characteristics, calculate the value of trans-conductance  $(g_m)$

12. And also calculate Amplification factor ( $\mu$ ).

#### **Observation:**

### **Drain Characteristics**

| Sr. | $V_{GS} =$          | volts               | $V_{GS} =$          | volts               | $V_{GS} =$          | volts               |

|-----|---------------------|---------------------|---------------------|---------------------|---------------------|---------------------|

| No. | V <sub>DS</sub> (V) | I <sub>D</sub> (mA) | V <sub>DS</sub> (V) | I <sub>D</sub> (mA) | V <sub>DS</sub> (V) | I <sub>D</sub> (mA) |

| 1   |                     |                     |                     |                     |                     |                     |

| 2   |                     |                     |                     |                     |                     |                     |

| 3   |                     |                     |                     |                     |                     |                     |

| 4   |                     |                     |                     |                     |                     |                     |

| 5   |                     |                     |                     |                     |                     |                     |

| 6   |                     |                     |                     |                     |                     |                     |

| 7   |                     |                     |                     |                     |                     |                     |

| 8   |                     |                     |                     |                     |                     |                     |

### **Transfer Characteristics:**

| Sr. | $V_{DS} =$  | volts               | $V_{DS} =$          | volts               | $V_{DS} =$  | volts               |

|-----|-------------|---------------------|---------------------|---------------------|-------------|---------------------|

| No. | $V_{GS}(V)$ | I <sub>D</sub> (mA) | V <sub>GS</sub> (V) | I <sub>D</sub> (mA) | $V_{GS}(V)$ | I <sub>D</sub> (mA) |

| 1   |             |                     |                     |                     |             |                     |

| 2   |             |                     |                     |                     |             |                     |

| 3   |             |                     |                     |                     |             |                     |

| 4   |             |                     |                     |                     |             |                     |

| 5   |             |                     |                     |                     |             |                     |

| 6   |             |                     |                     |                     |             |                     |

| 7   |             |                     |                     |                     |             |                     |

| 8   |             |                     |                     |                     |             |                     |

### Graph is plotted on graph paper

**Result:** The drain and transfer characteristics of FET is observed and the plotted on graph paper.

| AC drain resistance | $r_d =$          | ohm  |

|---------------------|------------------|------|

| Trans-conductance   | g <sub>m</sub> = | _mho |

Amplification factor $\mu =$ \_\_\_\_\_

**Signature of Faculty**

Date of Experiment

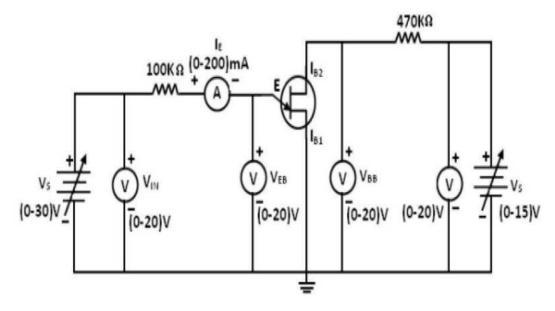

### **EXPERIMENT NO: 10**

Aim: To plot the V-I Characteristics of Unijunction Transistor (UJT).

**Apparatus Required**:

- 1. Regulated Power Supply (0-30V, 1A) 2Nos

- 2. UJT 2N2646

- 3. Resistors  $100k\Omega$ ,  $470k\Omega$

- 4. Voltmeter (0-30V) 2no

- 5. Ammeter (0-30mA) -1no.

- 6. Breadboard

- 7. Connecting Wires

**Theory:** A Unijunction Transistor (UJT) is an electronic semiconductor device that has only one junction. The UJT Unijunction Transistor (UJT) has three terminals an emitter (E) and two bases (B1 and B2). The base is formed by lightly doped n-type bar of silicon. Two ohmic contacts B1 and B2 are attached at its ends. The emitter is of p-type and it is heavily doped. The resistance between B1 and B2, when the emitter is open-circuit is called interbase resistance. The original unijunction transistor, or UJT, is a simple device that is essentially a bar of N type semiconductor material into which P type material has been diffused somewhere along its length. The 2N2646 is the most commonly used version of the UJT.

The UJT is biased with a positive voltage between the two bases. This causes a potential drop along the length of the device. When the emitter voltage is driven approximately one diode voltage above the voltage at the point where the P diffusion (emitter) is, current will begin to flow from the emitter into the base region. Because the base region is very lightly doped, the additional current (actually charges in the base region) causes (conductivity modulation) which reduces the resistance of the portion of the base between the emitter junction and the B2 terminal. This reduction in resistance means that the emitter junction is more forward biased, and so even more current is injected.

Overall, the effect is a negative resistance at the emitter terminal. This is what makes the UJT useful, especially in simple oscillator circuits. When the emitter voltage reaches  $V_p$ , the current starts to increase and the emitter voltage starts to decrease. This is represented by negative slope of the characteristics which is referred to as the negative resistance region, beyond the valley point,  $R_{B1}$  reaches minimum value and this region,  $V_{EB}$  proportional to  $I_E$ .

#### **Circuit Diagram:**

#### **Procedure:**

1. Connect the circuit as shown in above figure.

2. Keep  $V_{BB} = 5V$ , Vary  $V_{EB}$  smoothly with fine control such that  $V_E$  Varies in steps of 0.5 volts from zero and note down the resulting emitter current  $I_E$  for each step in the tabular form.

3. Repeat the experiment for  $V_{BB} = 7V$  and for  $V_{BB} = 10V$ .

4. Draw the graph between  $V_{EB}$  Vs  $I_E$  by keeping  $V_{BB}$  constant.

### **Observation:**

| Sr. | $V_{BB} =$          | volts               | $V_{BB} =$          | volts               | $V_{BB} =$          | volts               |

|-----|---------------------|---------------------|---------------------|---------------------|---------------------|---------------------|

| No. | V <sub>EB</sub> (V) | I <sub>E</sub> (mA) | V <sub>EB</sub> (V) | I <sub>E</sub> (mA) | V <sub>EB</sub> (V) | I <sub>E</sub> (mA) |

| 1   |                     |                     |                     |                     |                     |                     |

| 2   |                     |                     |                     |                     |                     |                     |

| 3   |                     |                     |                     |                     |                     |                     |

| 4   |                     |                     |                     |                     |                     |                     |

| 5   |                     |                     |                     |                     |                     |                     |

| 6   |                     |                     |                     |                     |                     |                     |

| 7   |                     |                     |                     |                     |                     |                     |

| 8   |                     |                     |                     |                     |                     |                     |

Graph is plotted on graph paper

**Result:** The V-I Characteristics of UJT is plotted on graph paper.

**Signature of Faculty**